VG7050CDN VOLTAGE -CONTROLLED CRYSTAL OSCILLATOR(VCXO) OUTPUT:CMOS

- Frequency range

:85 MHz to 170 MHz

- Supply voltage

:3.3 V Typ.

- Absolute Pull Range

:± 50 × 10-6 Min

- Operation temperature

:-40 °C to +85 °C:-40 °C to +105 °C

- External dimensions

:7.0 × 5.0 × 1.5 mm

- Output

:CMOS

- Function

:Output Enable(OE)

(High-Frequency Fundamental)

![]()

![]()

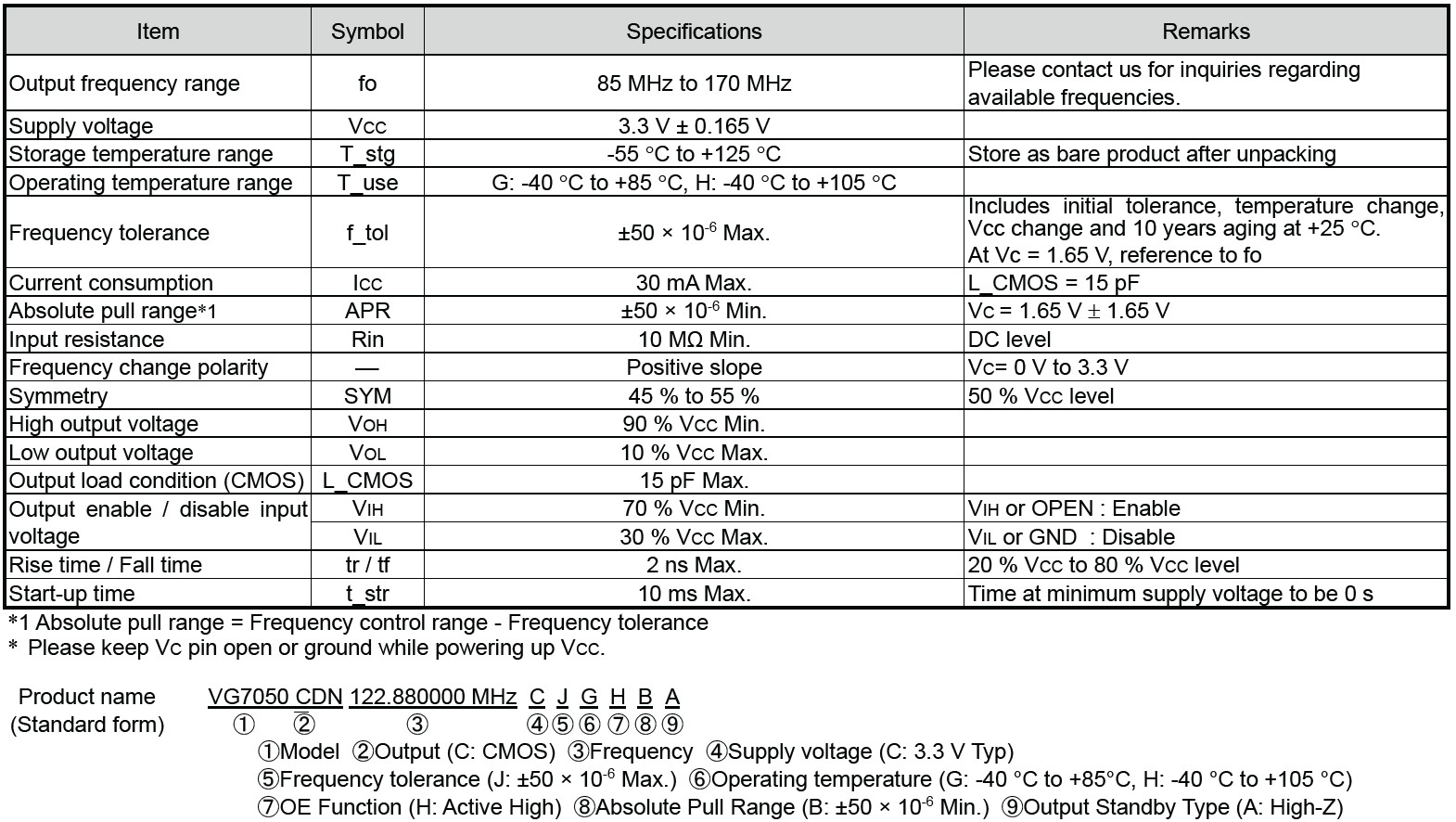

VG7050CDN

Specifications (characteristics)

External dimensions

(Unit: mm)

Note.

OE Pin

OE pin = "H" or "Open" : Specified frequency output.

OE pin = "L" : Output is high impedance.

Footprint (Recommended)

(Unit: mm)

In order to achieve optimum jitter performance, it is recommended that the capacitor (0.1 µF + 10 µF)

between VCC and GND pin should be placed as close to the VCC pin as possible.