VG7050EAN Programmable Voltage Controlled Oscillator (VCXO)Output: LV-PECL

- Frequency range

50 MHz to 800 MHz (Tuning resolution:2.2~2.8 x 10-9)

- Supply voltage

2.5 V / 3.3 V

- External dimensions

7.0 × 5.0 × 1.5 mm (8pins)

- Absolute Pull Range

±0~±180 x 10-6(12steps selectable)

- Features

- User-specified one startup frequency

- APR and 7-bit I2C address

- User Programming: I2C Interface

- Low jitter PLL technology

- Applications

SONET/SDH, OTN, GbE, Fibre Channel

![]()

![]()

VG7050EAN

Design Support Data Download

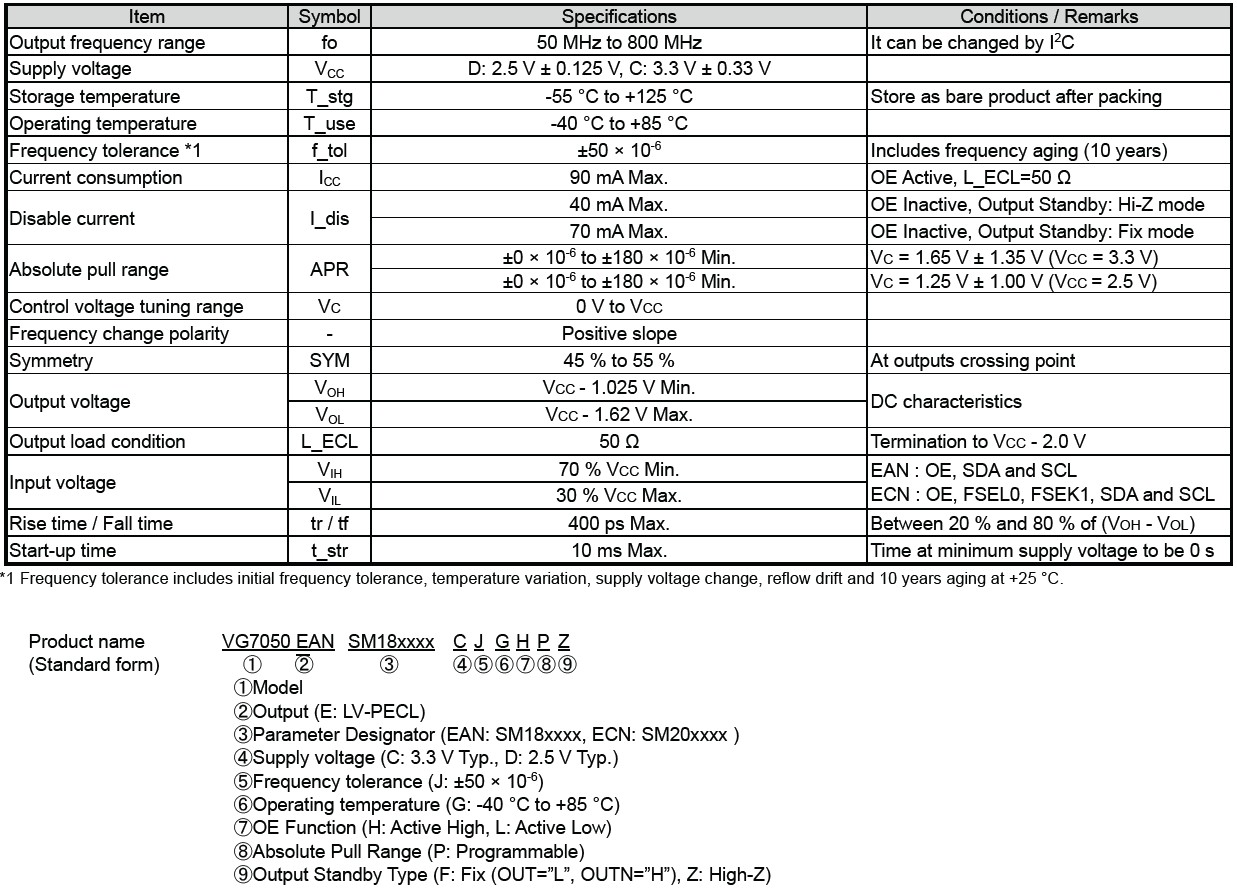

Specifications (characteristics)

Phase Jitter

| Offset Frequency | 125.00 MHz | 156.25 MHz | 250.00 MHz | 425.00 MHz | 622.08 MHz | 669.33 MHz | 794.73 MHz | |

|---|---|---|---|---|---|---|---|---|

| Phase jitter*2 Typ. |

12 kHz to 20 MHz | 0.30 ps | 0.26 ps | 0.26 ps | 0.25 ps | 0.26 ps | 0.26 ps | 0.26 ps |

| 20 kHz to 50 MHz | 0.30 ps | 0.27 ps | 0.27 ps | 0.26 ps | 0.27 ps | 0.27 ps | 0.27 ps | |

| 50 kHz to 80 MHz | 0.29 ps | 0.27 ps | 0.27 ps | 0.26 ps | 0.27 ps | 0.27 ps | 0.27 ps |

*2. In order to achieve optimum jitter performance, it is recommended that the capacitor (0.1 µF + 10 µF) between VCC-GND pin should be placed as close to the VCC pin as possible.

Block diagram

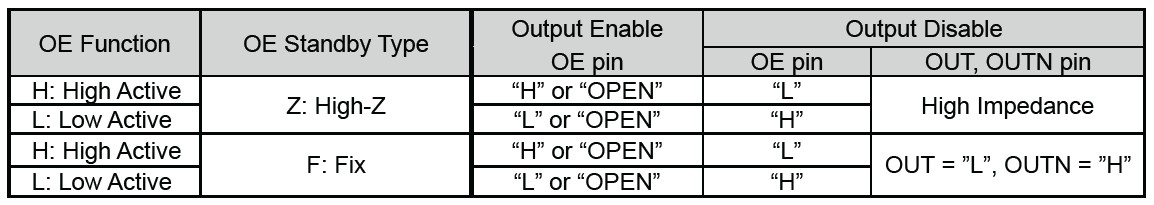

OE Function / OE Standby Type

External dimensions

(Unit: mm)

Footprint (Recommended)

(Unit: mm)

In order to achieve optimum jitter performance, it is recommended that the capacitor (0.1 µF + 10 µF)

between VCC and GND pin should be placed as close to the VCC pin as possible.